- 您现在的位置:买卖IC网 > Sheet目录1253 > XGBE-XGXS-O4-N2 (Lattice Semiconductor Corporation)IP CORE 10GBE ETHERNET XGXS

�� �

�

Lattice� Semiconductor�

�10Gb� Ethernet� XGXS� IP� Core� User’s� Guide�

�I/O� Signal� Descriptions�

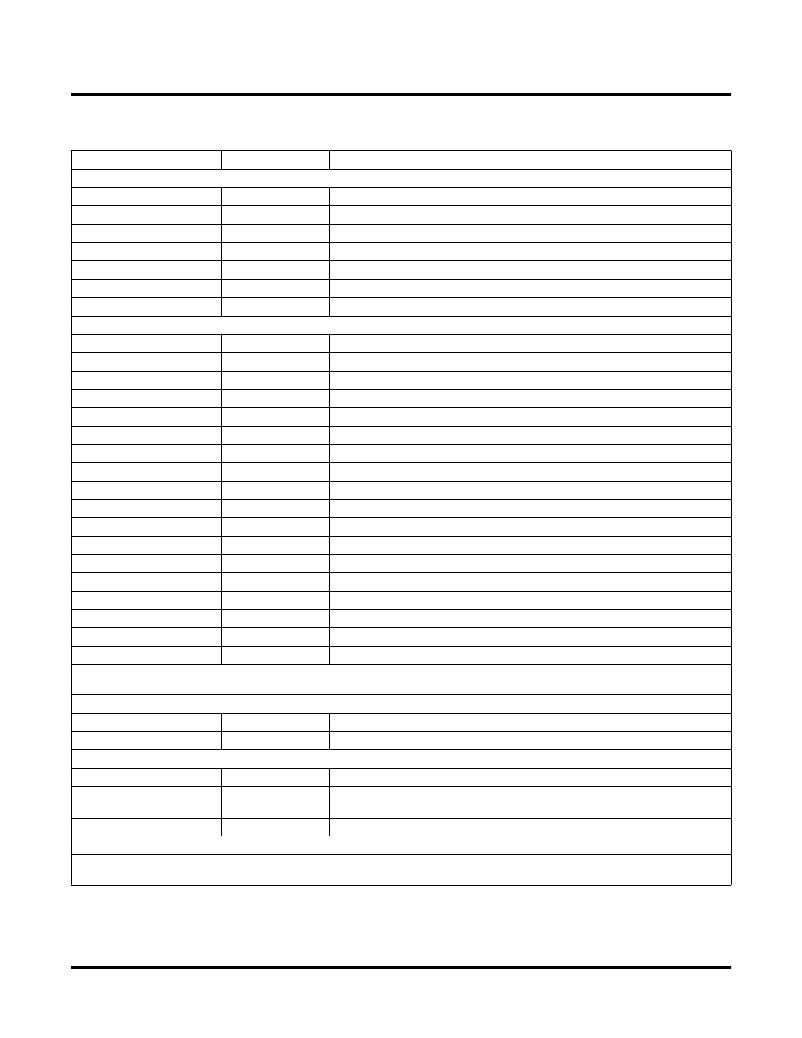

�Table� 10.� XGXS� Solution� I/O�

�Signal� Name�

�Direction�

�Description�

�XGMII� Signals�

�xgmii_tx_data[31:0]�

�input�

�32-bit� wide� DDR� XGMII� input� data.�

�xgmii_tx_ctrl[3:0]�

�input�

�Per-byte� DDR� XGMII� control� inputs.�

�xgmii_txclk_156�

�input�

�156MHz� XGMII� transmit� (XGXS� input)� clock.�

�xgmii_rx_data[31:0]�

�output�

�32-bit� wide� DDR� XGMII� output� data.�

�xgmii_rx_ctrl[3:0]�

�output�

�Per-byte� DDR� XGMII� control� outputs.�

�xgmii_rxclk_156�

�input�

�XGMII� receive� (XGXS� output)� reference� clock.�

�xgmii_rxclk_156_out�

�output�

�Forwarded� XGMII� receive� (XGXS� output)� clock.�

�XAUI� Signals�

�HDINN_BA�

�input�

�High-speed� CML� receive� data� input� -� SERDES� quad� B,� channel� A.�

�HDINP_BA�

�input�

�High-speed� CML� receive� data� input� -� SERDES� quad� B,� channel� A.�

�HDINN_BB�

�input�

�High-speed� CML� receive� data� input� -� SERDES� quad� B,� channel� B.�

�HDINP_BB�

�input�

�High-speed� CML� receive� data� input� -� SERDES� quad� B,� channel� B.�

�HDINN_BC�

�input�

�High-speed� CML� receive� data� input� -� SERDES� quad� B,� channel� C.�

�HDINP_BC�

�input�

�High-speed� CML� receive� data� input� -� SERDES� quad� B,� channel� C.�

�HDINN_BD�

�input�

�High-speed� CML� receive� data� input� -� SERDES� quad� B,� channel� D.�

�HDINP_BD�

�input�

�High-speed� CML� receive� data� input� -� SERDES� quad� B,� channel� D.�

�HDOUTN_BA�

�output�

�High-speed� CML� transmit� data� output� -� SERDES� quad� B,� channel� A.�

�HDOUTP_BA�

�output�

�High-speed� CML� transmit� data� output� -� SERDES� quad� B,� channel� A.�

�HDOUTN_BB�

�output�

�High-speed� CML� transmit� data� output� -� SERDES� quad� B,� channel� B.�

�HDOUTP_BB�

�output�

�High-speed� CML� transmit� data� output� -� SERDES� quad� B,� channel� B.�

�HDOUTN_BC�

�output�

�High-speed� CML� transmit� data� output� -� SERDES� quad� B,� channel� C.�

�HDOUTP_BC�

�output�

�High-speed� CML� transmit� data� output� -� SERDES� quad� B,� channel� C.�

�HDOUTN_BD�

�output�

�High-speed� CML� transmit� data� output� -� SERDES� quad� B,� channel� D.�

�HDOUTP_BD�

�output�

�High-speed� CML� transmit� data� output� -� SERDES� quad� B,� channel� D.�

�REFCLKP_B�

�input�

�SERDES� Quad� B� reference� clock.�

�REFCLKN_B�

�input�

�SERDES� Quad� B� reference� clock.�

�Please� refer� to� the� ORT82G5� Data� Sheet� for� additional� information� on� con?guring� the� SERDES� interface� for� speci?c� applica-�

�tions.�

�MDIO� Interface� Signals�

�mdio�

�input/output�

�MDIO� bi-directional� data.�

�mdc�

�input�

�MDIO� clock.�

�XGXS� Soft� IP� Control� and� Status� Signals�

�reset_n�

�input�

�XGXS� programmable� core� reset� (active� low).�

�pwrup_init_en�

�input�

�Enable� automatic� con� ?� guration� of� embedded� core� (active� high� -� see� Sec.� 2.7�

�for� details).�

�inj_err_n�

�input�

�Inject� error� (active� low� -� see� Sec.� 2.6� for� details).�

�ORT82G5� Embedded� Core� Control,� Global� I/O� and� FPGA� Con� ?� guration� I/O�

�Please� refer� to� the� ORCA� Series� 4� FPGA� Data� Sheet� and� the� ORT82G5� Data� Sheet� for� information� on� the� various� con?gura-�

�tion� options.�

�22�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

XM2D-0901

CONNECTOR

XM2D-3701

CONNECTOR

XM4M-2432-1312

CONN DVI 24POS 1.5A 40V DIGITAL

XM4M-2932-1311

CONN DVI 29POS 1.5A DIGTL/ANALOG

XM7B-0442

CONN USB 1A 30VAC R/A WHITE

XOCLCC6EVB

EVAL BOARD FOR XOCLCC6

XR16M890IL32-0C-EB

BOARD EVAL XR16M890IL32

XR18W750/753-0B-EB

EVAL BOARD FOR XR18W750/753

相关代理商/技术参数

XGC

制造商:Excelsys Technologies 功能描述:Power Suply, 36V@5.6A, Open Frame, Cage Mount, Modular, UltiMod Series 制造商:Excelsys Technologies 功能描述:MODULE POWER 28.8V-39.6V 5.6A

XGC10-88-S20

制造商:Johnson Electric / Saia-Burgess 功能描述:Catalogue / XGC10-88-S20 制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XGC10-88-S20

XGC11-88-S20

制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XGC11-88-S20

XGC11-88-S20Z1

制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XGC11-88-S20Z1

XGC11-88-S40

制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XGC11-88-S40

XGC12-81Z1

制造商:Johnson Electric / Saia-Burgess 功能描述:Catalogue / XGC12-81Z1

XGC12-88

制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XGC12-88

XGC12-88-J23

制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XGC12-88-J23